9-ASKA 20241101

Written by: Paul Lowndes <[email protected]>

Table of Contents

Decentralized Mesh Networking

Decentralized Mesh Network on Chip (DMNoC)

Patent Title: Hierarchical Decentralized Mesh Network on Chip for Secure Multi-Kernel Architectures

Title: Hierarchical Decentralized Mesh Network on Chip with Dynamically Configurable Security Zones for Secure Multi-Kernel Computing

ASKA Enhancement Proposal: Decentralized Mesh Network on Chip (DMNoC)

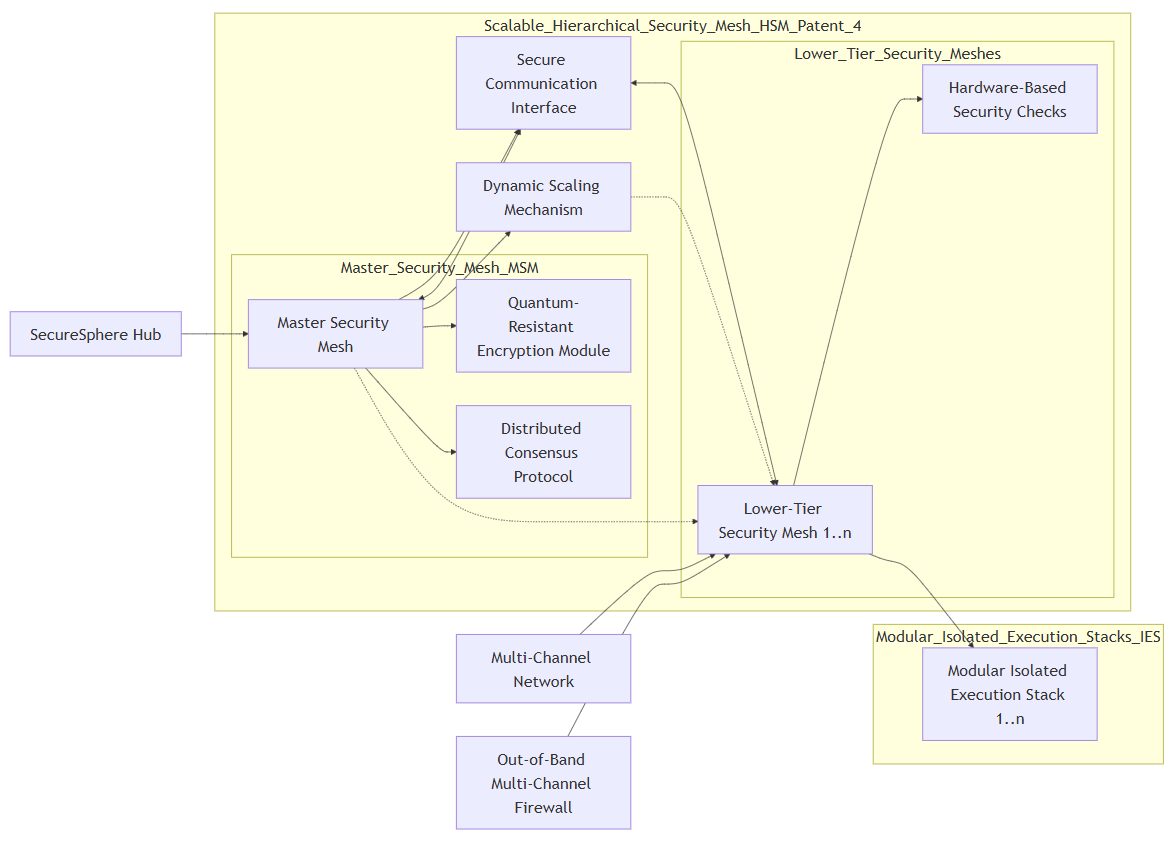

PATENT 4 DIAGRAM

xBGAS is a RISC-V ISA extension designed to improve the performance of remote memory accesses in large-scale HPC systems.

Intel’s CET inspiration for ASKA

Further inspirations from CET and xBGAS for ASKA, via more speculative or advanced concepts:

Capabilities Basics for ASKA

CheriOS inspirations

Tyche Inspirations

IskiOS inspirations

Rhodes OS inspirations

Kernel Driver Inspiration

FlexOS

Unikraft inspiration

Hyperkernel insights 1 of 2

Hyperkernel 2 of 2 (amateur)

Decentralized Mesh Networking

graph

subgraph "ASKA Instance (Local)"

subgraph "DMNoC (Decentralized Mesh NoC)"

FA_1["Fiber Adapter 1"] --> Switch_1["NoC Switch 1"]

FA_2["Fiber Adapter 2"] --> Switch_2["NoC Switch 2"]

FA_N["Fiber Adapter N"] --> Switch_N["NoC Switch N"]

Switch_1 <--> Switch_2

Switch_1 <--> Switch_N

Switch_2 <--> Switch_N

subgraph "IES Access Points (Isolated)"

direction LR

Switch_1 --> IES1["IES 1"]

Switch_N --> IESn["IES n"]

IES1 --> App1["Application 1"]

IESn --> AppN["Application N"]

end

Attestation["Hardware Attestation<br>(3D Microstructures)"] --> DLT["Decentralized Ledger<br>(ASKA Instance)"]

Switch_1 --> Attestation

Switch_N --> Attestation

end

subgraph ASKA Integration

DMNoC --> PolicyEngine["Policy Engine (P4)"]

DMNoC <--> DTMS["DTMS (P4)"]

DMNoC --> ResourceMgr["Resource Manager<br>(P9,P10)"]

LocalMSM["Local MSM (P2)"] -.-> DMNoC

AESDS["AESDS (P16)"] --> DMNoC

end

subgraph "External Secure Channels (P3, P5)"

direction LR

Channel1["Secure Channel 1"] --> Ext_SS1["External ASKA 1"]

ChannelN["Secure Channel N"] --> Ext_SSN["External ASKA N"]

DMNoC --> Channel1

DMNoC --> ChannelN

IAMA["IAMA (P16)"] --> DMNoC

end

End

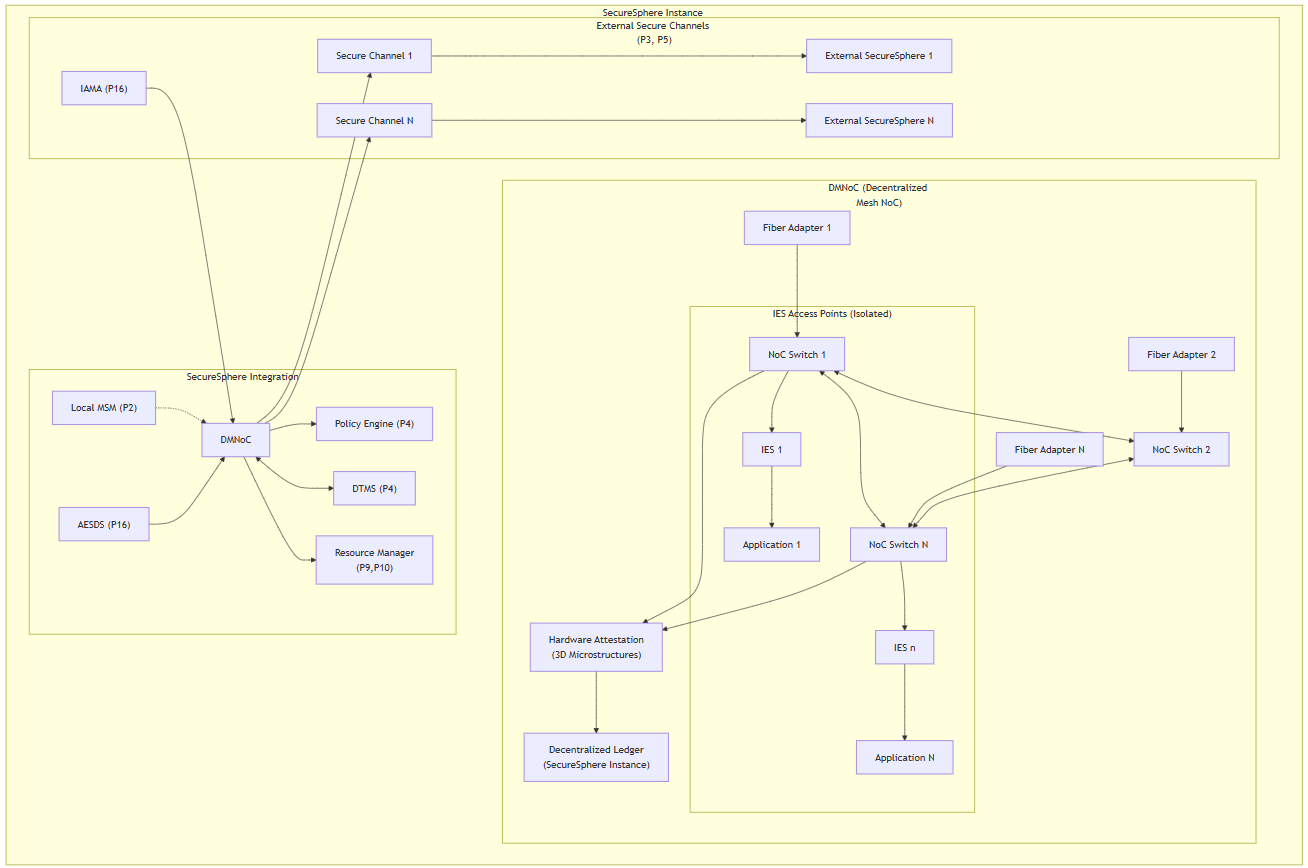

Diagram Explanation and Justification:

- ASKA Instance (Local): This represents the local ASKA instance containing the DMNoC.

- DMNoC (Decentralized Mesh NoC): This subgraph details the core of the innovation.

- Fiber Adapters (FA_1, FA_2, FA_N): These adapters connect the DMNoC to external fiber channel networks, providing high-bandwidth connectivity for each of the (up to N) external ASKA instances.

- NoC Switches: The switches within the DMNoC create the mesh network topology, routing data between fiber adapters and IES access points. The interconnected switches provide redundancy and fault tolerance.

- IES Access Points (Isolated): Each IES instance has dedicated, hardware-isolated access points to the DMNoC. This maintains ASKA's core principle of isolation and prevents unauthorized access. The connections between the switches and IES instances are managed dynamically through the switching fabric and controlled by the Policy Engine (P4).

- Hardware Attestation (3D Microstructures): Each fiber adapter and switch within the DMNoC undergoes hardware attestation using 3D microstructures. This ensures the integrity of the NoC components and prevents the introduction of malicious or counterfeit hardware.

- Decentralized Ledger (DLT): The attestation results are logged on the local ASKA instance's DLT for secure record-keeping and auditing. External instances can access this DLT (with appropriate permissions) to validate the local instance's NoC components before initiating communication. This facilitates trust between ASKA instances and helps maintain the system's security despite the expanded attack surface of each IES instance.

- ASKA Integration: This subgraph highlights how the DMNoC integrates with ASKA's existing security components:

- Policy Engine (P4): Controls access to the DMNoC and manages routing policies within the mesh network using dynamically generated and updated policies (based on analysis of events, trust scores, anomalies detected by the AI agent swarms, and external threat intelligence reports) enforced through each network interface, ensuring that all data transmitted is fully compliant with security regulations and organizational policy. This also ensures that only authorized system components or applications can communicate through the DMNoC and restricts traffic from any nefarious clients, including compromised IES instances, through revocation of access controls and use of other ASKA security mechanisms such as HESE-DAR and MDATS for additional protections on these sensitive data sources.

- DTMS (P4): Provides dynamic trust information that influences the routing decisions and access control policies within the DMNoC. Trust levels for both internal and external ASKA instances (and Zones) are continuously updated and leveraged, enabling more dynamic real-time adjustments and configurations.

- Resource Manager (P9, P10): Manages resource allocation related to the DMNoC (e.g., bandwidth allocation for different communication channels).

- Local MSM (P2): Monitors the DMNoC for anomalies and security breaches, providing feedback to the DTMS and Policy Engine. The unidirectional connection prevents the MSM from being compromised by a potentially compromised DMNoC.

- AESDS (P16): Manages secure software updates for the DMNoC components (switches, adapters, etc.), ensuring that the NoC's firmware is up-to-date and incorporating any necessary security patches. This ensures the integrity of the NoC software.

- External Secure Channels (P3, P5): This subgraph shows how the DMNoC enables secure communication with external ASKA instances.

- Secure Channels: Each external ASKA instance connects to the DMNoC via dedicated, secure channels that use authenticated and encrypted communication (P3, P5) with quantum key exchange where appropriate, minimizing risks during information transfer to and from external ASKA deployments while enabling real-time, two-way communication streams for AI agent swarming and collaboration across the secure network. This allows security systems and policies to be deployed dynamically based on various conditions, including threat assessments, system performance, available resources, and consensus between nodes on high-priority actions with detailed logging and auditing of events that use these capabilities to support forensic analysis in case of a potential or actual breach. Further, the AI Agent can leverage external services or cloud-based security providers like SDE and FL for secure offloading of some analysis to help minimize performance bottlenecks without the data leaving ASKA. External ASKA instances may also have different levels of trust and policies based on access rights within and across Zones or devices, and those access control parameters can be dynamically managed and adjusted using existing capabilities described earlier for enhanced security and trust throughout the secure network.

- IAMA (P16): IAMA analyzes the security posture of external ASKA instances and their associated NoC components (using the attestation information logged on their respective DLTs), helping prevent interactions with potentially compromised external instances and providing proactive security assessments and threat predictions for each external node (and their zones within) connected to ASKA’s NoC to inform the Policy Engine and alert the security teams. This continuous monitoring enhances trust by creating a dynamic risk profile for each connected entity on the network, strengthening the resilience of the DMNoC and ASKA against sophisticated multi-zone or multi-instance coordinated attacks.

Decentralized Mesh Network on Chip (DMNoC)

This document proposes a Decentralized Mesh Network on Chip (DMNoC) to enhance ASKA's communication capabilities. While ASKA's architecture already incorporates a secure multi-channel network (MCN - P3), the DMNoC introduces valuable new concepts and enhancements.

Key Concepts and ASKA Relevance:

- Motivation for DMNoC: The document correctly identifies scalability and resilience as crucial challenges for ASKA’s network as the number of connected devices and data streams increases. The DMNoC's proposed benefits (increased bandwidth, enhanced security, improved scalability) align with ASKA's goals. The DMNoC's focus on providing high-bandwidth, low-latency communication is particularly relevant for decentralized ledger performance, secure inter-zone collaboration (SIZCF - P22), and AI agent swarming.

- Proposed DMNoC Architecture: The proposed architecture incorporates several key features:

- Decentralized Mesh Topology: The decentralized mesh topology provides redundancy and fault tolerance, which is crucial for ASKA's resilience. The dynamic routing algorithms, optimized for secure path selection, align with ASKA's adaptive security model.

- Hardware Isolation: The hardware isolation of IES access points to the DMNoC maintains ASKA's core principle of isolation. The dynamic management of connections between switches and IES instances, controlled by the Policy Engine (P4), aligns with ASKA’s dynamic adaptability.

- Microstructure Authentication and DLT Integration: The use of 3D microstructures for hardware attestation and the integration with the Decentralized Ledger enhance the DMNoC's security and trustworthiness. This complements ASKA’s existing security mechanisms. The independent verification is a notable benefit.

- ASKA Integration: The proposed integration with existing ASKA components is well-considered:

- DTMS (P4): Using dynamic trust levels to influence routing and access control aligns with ASKA's core principles.

- Policy Engine (P4) and AESDS (P16): Leveraging the Policy Engine for access control and AESDS for secure software updates ensures that the DMNoC is managed securely.

- Resource Borrowing: The potential for hardware-level resource borrowing through the DMNoC is a valuable enhancement, creating new possibilities for resource sharing.

- Hardware Security Systems: The integration with LSMs and the Secure UI Kernel reinforces ASKA's layered security approach.

- IAMA (P16): Using IAMA to analyze the security posture of external ASKA instances and prevent interactions with compromised instances is a critical security feature.

Novel Idea for ASKA:

The proposed DMNoC architecture is already a novel enhancement for ASKA, introducing a decentralized, high-bandwidth, and secure on-chip network. However, the concept can be further refined with the following novel approach:

- Hierarchical DMNoC with Dynamically Configurable Security Zones: ASKA could implement a hierarchical DMNoC, where each IES instance has its own dedicated sub-mesh, interconnected with other sub-meshes through secure gateways. These gateways would enforce access control policies based on capabilities (P25) and trust levels (P4) and dynamically filter traffic based on security assessments from the Security Mesh (P2) and the AI Agent (P36). The sub-meshes could be further divided into security zones with different trust levels, creating a highly granular and adaptable security architecture within the DMNoC. This enhances the following:

- Enhanced Isolation: This approach would significantly enhance ASKA’s isolation capabilities by providing fine-grained network segmentation within each IES instance using physical hardware rather than logical or software-based mechanisms. This is similar to how security zones are created in ASKA, but now those zones extend to the network layer itself too at a very fine granularity. This would enhance protection against lateral movement of attacks and improve containment of security breaches within the DMNoC without necessarily requiring any additional hardware within ASKA (e.g., by leveraging existing components for the fiber channel network interfaces), minimizing costs and complexity.

- Dynamic Reconfiguration: The AI Agent (P36) and the Policy Engine (P4) could dynamically reconfigure the security zones and gateway policies based on real-time threat assessments and workload demands, providing adaptive security at the network level within and across IES instances and ASKA zones. The AESDS would securely deploy these updates and reconfigurations (P16). This dynamic adjustment of trust boundaries within the NoC will enhance ASKA’s response time to attacks from other modules (including drivers, compromised systems), by allowing the system to isolate vulnerable segments immediately and automatically without involving manual oversight or external intervention. This also provides additional flexibility, improving its ability to dynamically balance performance against security tradeoffs.

- Simplified Management: The hierarchical structure would simplify network management and policy enforcement, as policies could be defined at different levels of the hierarchy, improving efficiency while also enabling greater control over the most crucial parameters related to security on ASKA.

- Scalability and Resilience: The hierarchical DMNoC, combined with the mesh topology, would enhance ASKA’s scalability and resilience to security breaches. This architecture will minimize bottlenecks as the system grows while ensuring high availability, even in the presence of node or network failures.

- Integration with Existing Mechanisms: This approach leverages and integrates seamlessly with ASKA’s core technologies, including IES isolation, dynamic trust management (P4), the Security Mesh (P2), capability-based access control (P25, P26), and AI-driven adaptation. The use of dedicated hardware, combined with the existing ASKA security mechanisms, would provide a robust and highly-secure NoC architecture that further enhances the integrity, availability and security of the Decentralized Ledger from those threats posed by a hostile network environment, or potentially malicious software. It improves the ability for a third party to securely audit activity because of the enhanced data provenance and tamper-evident safeguards.

This hierarchical DMNoC, with its dynamic security zones, would significantly enhance ASKA's security posture by preventing lateral movement of attacks, providing fine-grained access control at the network level, and enabling adaptive response to threats in a decentralized hardware OS environment. It represents a natural extension of ASKA's existing security principles and technologies, offering a compelling and unified solution.

graph LR

subgraph ASKA Instance

direction LR

subgraph IES Instance 1

SubMesh1["IES 1 Sub-mesh<br>(Dynamic Security Zones)"] --> Gateway1["Secure Gateway"]

end

subgraph IES Instance 2

SubMesh2["IES 2 Sub-mesh<br>(Dynamic Security Zones)"] --> Gateway2["Secure Gateway"]

end

subgraph IES Instance N

SubMeshN["IES n Sub-mesh<br>(Dynamic Security Zones)"] --> GatewayN["Secure Gateway"]

end

Gateway1 --> DMNoC["Hierarchical DMNoC<br>(Routing & Switching)"]

Gateway2 --> DMNoC

GatewayN --> DMNoC

subgraph DMNoC Internals

Switch1["Switch 1"] <--> Switch2["Switch 2"]

Switch2 <--> SwitchN["Switch N"]

SwitchN <--> Switch1

Switch1 --> FiberChannel1["Fiber Channel 1<br>(External)"]

SwitchN --> FiberChannelN["Fiber Channel N<br>(External)"]

end

end

style DMNoC fill:#ccf,stroke:#333,stroke-width:2px

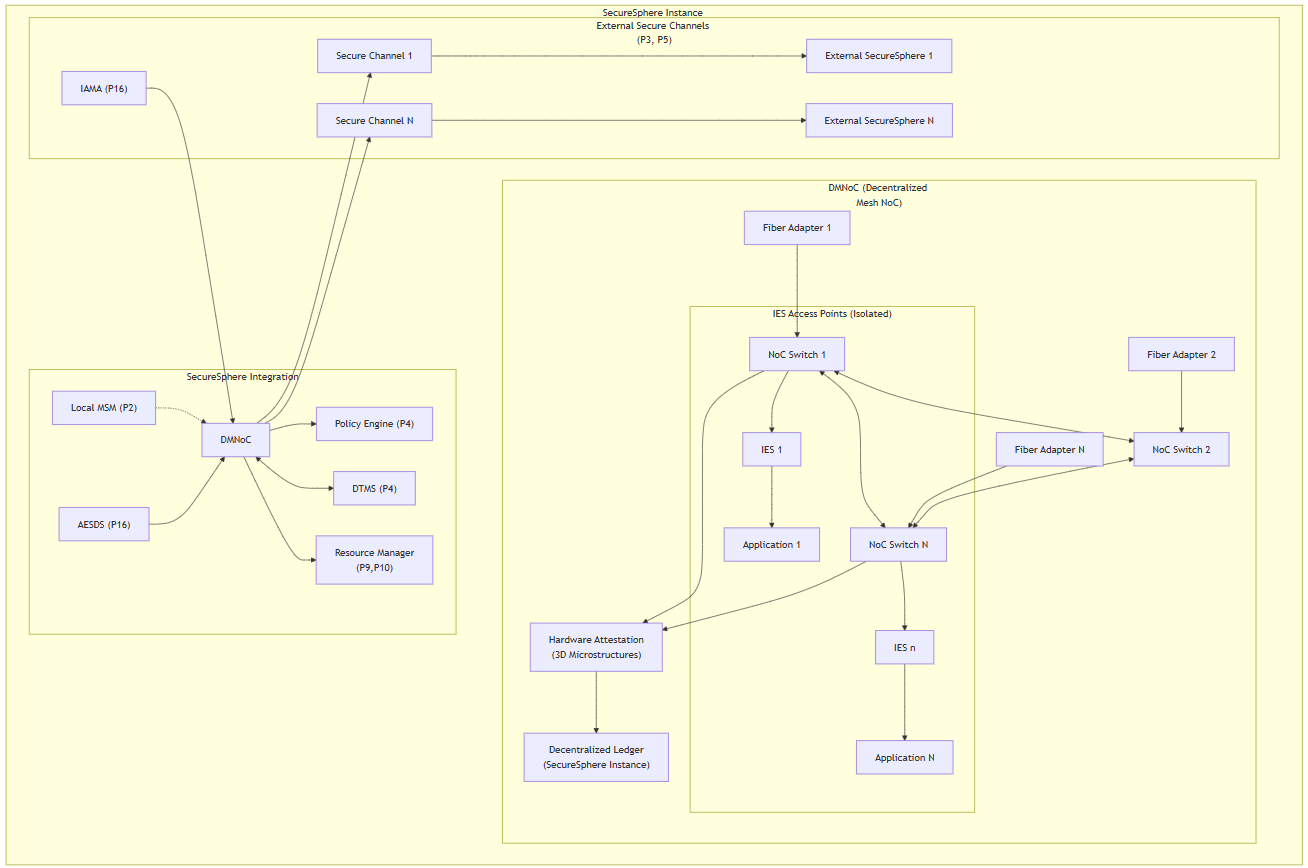

Diagram Explanation and Justification:

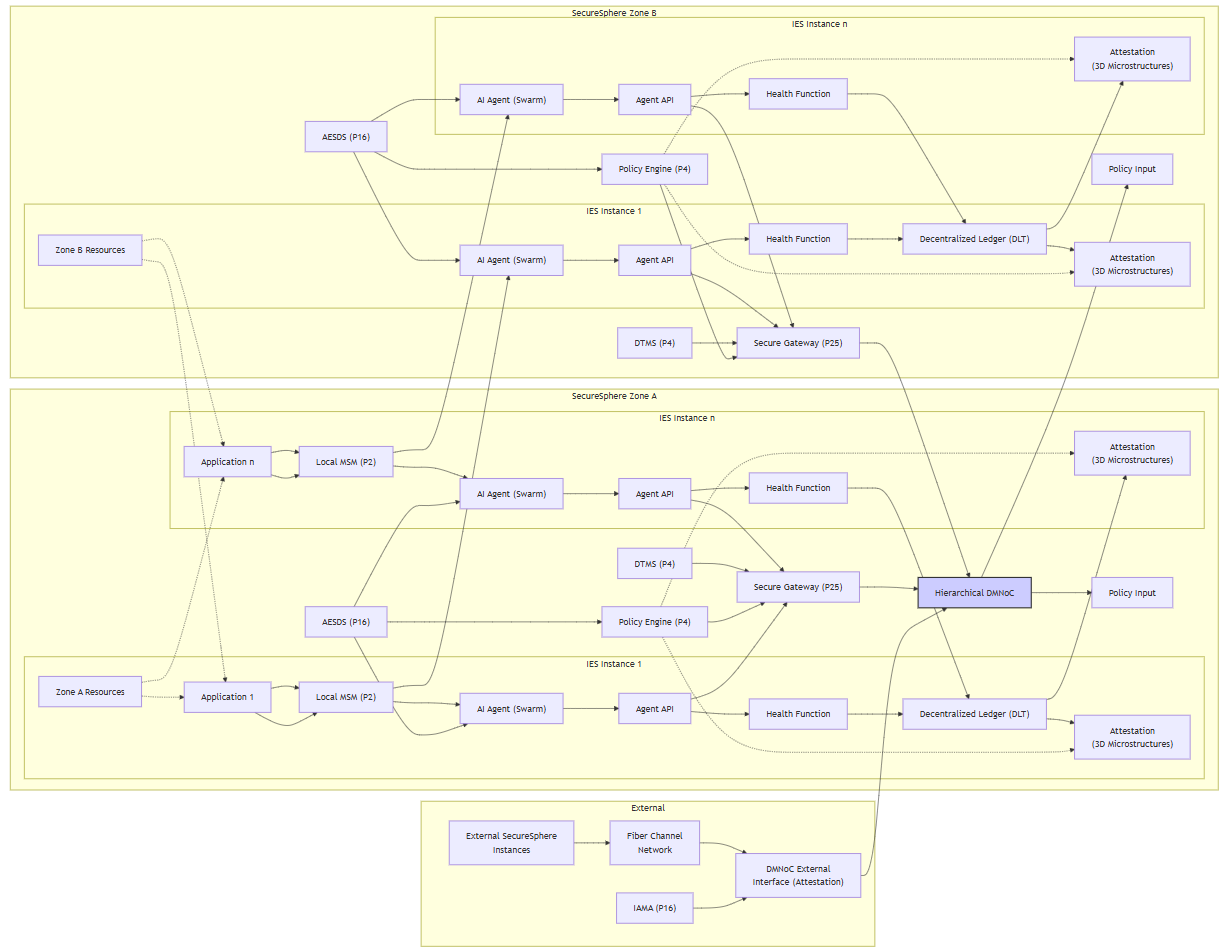

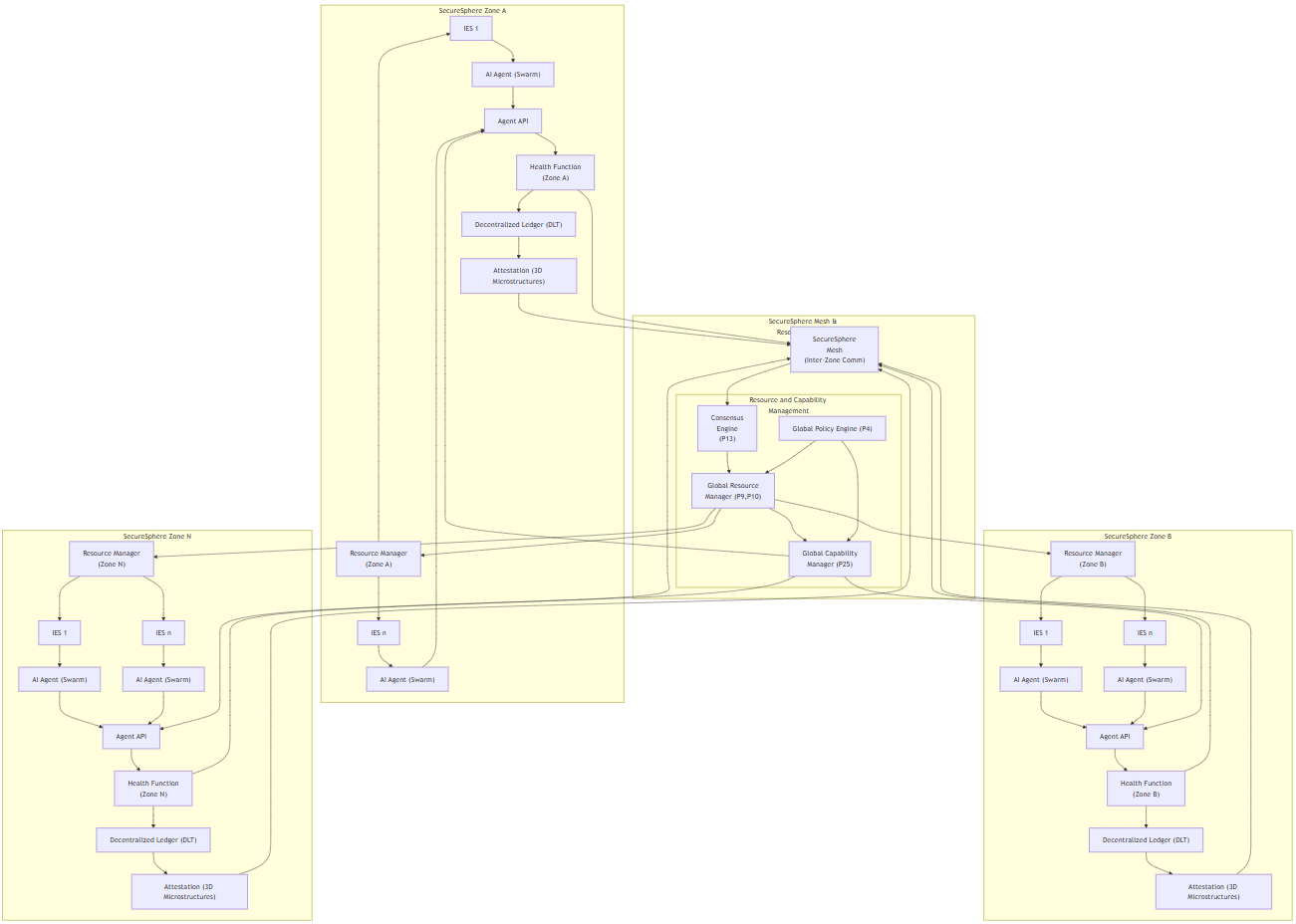

This diagram provides a detailed view of the Hierarchical DMNoC, focusing on its integration with ASKA's security mechanisms and its role in secure resource sharing. It builds upon the previous diagram by showing the internals of each zone and how they connect to the DMNoC.

- ASKA Zones (A, B): Two zones are depicted, each with multiple IES instances, AI agent swarms, and associated components. This emphasizes the decentralized nature of the architecture.

- IES Instances and Internal Components: Within each zone, the diagram details the components of an IES instance:

- Applications (App1, AppN): Represent applications running within the IES.

- Local MSM (P2): Monitors resource access and system behavior within the IES.

- AI Agent (Swarm): Represents the swarm of AI agents within the IES, analyzing data from the LSM.

- Agent API: Provides a secure interface for communication with other components.

- Health Function: Assesses the health of the IES and its resources.

- DLT: Logs health and attestation data.

- Attestation (3D Microstructures): Represents the hardware attestation process for each IES using 3D microstructures.

- Zone Resources: The dotted lines from "Zone A Resources" and "Zone B Resources" indicate the resources (CPU, memory, etc.) available to the applications and other components within each zone.

- Secure Gateway (P25): Each IES instance connects to the DMNoC through a Secure Gateway. This gateway uses capabilities (P25) to enforce access control and prevent unauthorized communication between IES instances and the larger DMNoC. The gateway receives information from the local Policy Engine, the local DTMS and forwards policy configuration information into the DMNoC. It also aggregates requests from AI Agents and Health Monitors for optimized, secure information exchange.

- Hierarchical DMNoC: The central DMNoC is depicted, highlighting its hierarchical structure by showing the connections from the Secure Gateways. It receives attestation information and manages communication and resource sharing between Zones through its internal routing and switching fabric, leveraging existing secure communication channels and policies.

- Policy Engine and AESDS: Within each Zone, the Policy Engine (P4) and AESDS (P16) interact with the Secure Gateway and other security components. The Policy Engine receives input from the DMNoC and enforces policies for all cross-zone communications and resource sharing requests. AESDS is responsible for secure software updates for the AI Agents and other components within the zone. The dotted lines from the Policy Engine to the Attestation modules signify that the Policy Engine evaluates attestation results.

- External Interface and IAMA: The right side shows how external ASKA instances connect to the DMNoC:

- External ASKA Instances: Represent external ASKA deployments.

- Fiber Channel Network: This represents the high-bandwidth connection between ASKA instances, which can span large distances and support thousands of devices across the mesh.

- DMNoC External Interface (Attestation): The external interface of the DMNoC handles communication with the fiber channel network and performs attestation of external ASKA instances using information obtained from the DLT and associated 3D Microstructures. The attestation process verifies the cryptographic identity of the external instances and checks for malicious code from AESDS generated configurations. This ensures the integrity of external connections.

- IAMA (P16): IAMA plays a key role in analyzing the security posture of external instances and preventing interactions with potentially compromised systems, feeding its analysis and recommendations into the AI Agents, Policy Engine and the Decentralized Ledger in its Zone to update the security status of the associated external node. This proactive security measure enhances the DMNoC's robustness against attacks originating from external connections, leveraging ASKA's integrated security features.

This diagram enhances the previous visualization by showing the specific details of how the hierarchical DMNoC enables secure collaboration between zones and manages resource sharing while protecting sensitive internal components and external interfaces in ASKA using its existing security features and modules. The data flow and security mechanisms are clearly illustrated, along with the integration points with existing ASKA components. It provides sufficient technical detail for use in patent applications or technical discussions with AI engineers who may work on ASKA using specialized tools to implement or extend ASKA or its associated security infrastructure.

Drawing 3 of 3:

graph

subgraph ASKA Zone A

IES_A1[IES 1] --> Agent_A1["AI Agent (Swarm)"]

IES_An[IES n] --> Agent_An["AI Agent (Swarm)"]

Agent_A1 --> API_A["Agent API"]

Agent_An --> API_A

API_A --> Health_A["Health Function<br>(Zone A)"]

Health_A --> DLT_A["Decentralized Ledger (DLT)"]

DLT_A --> Attestation_A["Attestation (3D Microstructures)"]

ResMgr_A["Resource Manager<br>(Zone A)"] --> IES_A1

ResMgr_A --> IES_An

end

subgraph ASKA Zone B

direction LR

IES_B1[IES 1] --> Agent_B1["AI Agent (Swarm)"]

IES_Bn[IES n] --> Agent_Bn["AI Agent (Swarm)"]

Agent_B1 --> API_B["Agent API"]

Agent_Bn --> API_B

API_B --> Health_B["Health Function<br>(Zone B)"]

Health_B --> DLT_B["Decentralized Ledger (DLT)"]

DLT_B --> Attestation_B["Attestation (3D Microstructures)"]

ResMgr_B["Resource Manager<br>(Zone B)"] --> IES_B1

ResMgr_B --> IES_Bn

end

subgraph ASKA Zone N

direction LR

IES_N1[IES 1] --> Agent_N1["AI Agent (Swarm)"]

IES_Nn[IES n] --> Agent_Nn["AI Agent (Swarm)"]

Agent_N1 --> API_N["Agent API"]

Agent_Nn --> API_N

API_N --> Health_N["Health Function<br>(Zone N)"]

Health_N --> DLT_N["Decentralized Ledger (DLT)"]

DLT_N --> Attestation_N["Attestation (3D Microstructures)"]

ResMgr_N["Resource Manager<br>(Zone N)"] --> IES_N1

ResMgr_N --> IES_Nn

end

subgraph "ASKA Mesh & Resource Sharing"

Attestation_A --> Mesh

Attestation_B --> Mesh

Attestation_N --> Mesh

Health_A --> Mesh

Health_B --> Mesh

Health_N --> Mesh

Mesh["ASKA<br>Mesh<br>(Inter-Zone Comm)"] --> Consensus["Consensus<br>Engine<br>(P13)"]

subgraph Resource and Capability Management

direction LR

Consensus --> GlobalRM["Global Resource<br>Manager (P9,P10)"]

GlobalRM --> GlobalCapMgr["Global Capability<br>Manager (P25)"]

GlobalPolicy["Global Policy Engine (P4)"] --> GlobalCapMgr

GlobalPolicy --> GlobalRM

end

GlobalRM --> ResMgr_A

GlobalRM --> ResMgr_B

GlobalRM --> ResMgr_N

GlobalCapMgr --> API_A

GlobalCapMgr --> API_B

GlobalCapMgr --> API_N

end

Diagram Explanation and Justification:

This diagram focuses on the crucial aspect of resource and capability management within the decentralized, mesh network-enhanced ASKA architecture. It builds upon the previous diagrams, adding the key components that bring the system together from an engineering perspective.

- ASKA Zones (A, B, N): As before, multiple zones are shown, each with its own IES instances, AI Agents, Health Functions, DLTs, and Attestations. Now, each Zone has a dedicated local Resource Manager, emphasizing local resource control within a zone.

- ASKA Mesh and Resource Sharing: The ASKA Mesh receives health and attestation data. The Consensus Engine (P13) is now more prominently labeled and centralized, playing a critical role in global decision-making based on input from ASKA Zones.

- Resource and Capability Management: This new central subgraph is the key addition for this diagram, providing the engineering details for how global resource allocation is managed:

- Global Resource Manager (P9, P10): This component receives instructions from the Consensus Engine and manages resource allocation across all zones. It makes decisions based on the health and attestation information from the Mesh, ensuring that resources are allocated efficiently and securely. It communicates with the local Resource Managers in each zone, providing high-level control and coordination. It also leverages existing ASKA systems for resource monitoring, dynamic partitioning and performance optimization as defined in earlier Patents. This decentralized approach enables adaptive and real-time resource management. This distributed, consensus-based strategy enhances security by mitigating the risk of a single compromised agent unilaterally taking over resources, and the integration with the local Resource Managers allows for more granular and efficient utilization. Further, we anticipate that it will also create new avenues and methods for high-speed resource sharing and allocation through this hardware-based pathway, further enhancing its potential usefulness and accelerating development of novel use cases.

- Global Capability Manager (P25): This new component is crucial. It works in conjunction with the Global Resource Manager, dynamically allocating and managing capabilities across zones. It receives input from the Global Policy Engine, ensuring that capability assignments are consistent with overall security policies. The Global Capability Manager interacts with the Agent APIs in each zone to distribute and revoke capabilities for AI agents and other ASKA components, providing a central point of control for fine-grained access to resources and functionalities across the entire mesh network. This decentralized, hardware-enforced approach to capability management enhances security and scalability while maintaining consistency with ASKA's security principles. The tamper-proof, non-disruptive monitoring from the LSM and Watcher Mesh ensures that the Global Capability Manager's actions and internal states, such as which capabilities are assigned to which agents or entities, are continuously tracked, validated and verified against security policies based on those from each Zone’s local policy engine, and the Policy Engine from the ASKA hub, using the existing system calls and other integrated security mechanisms from ASKA. These results are stored on a distributed immutable ledger (Patents P13,P15), enhancing accountability, facilitating audits, and enabling forensic analysis across all ASKA components and networks, in order to better understand the context of which security decisions were made, when and why. Moreover, the hierarchical design itself enables more customized and fine-tuned policies with minimal overhead while ensuring consistency and trustworthiness of capabilities, increasing usability and adoption through reducing complexity for managing capabilities across the ASKA network, which is crucial for enterprise adoption and thus for market expansion.

- Global Policy Engine (P4): Governs the high-level policies for resource and capability allocation across all zones. It provides input to both the Global Resource Manager and the Global Capability Manager, ensuring that all decisions are aligned with ASKA’s overall security objectives and with those of each Zone. The Policy Engine defines thresholds, rules, and constraints related to resource allocation, capability distribution, and security monitoring, thereby providing a unified framework for managing these crucial aspects of the ASKA network. The system leverages ASKA’s existing methods for dynamic policy deployment (P16, P2, P3) and auditing, including MDATS and the Decentralized Ledger, to ensure all updates are secure and traceable, enhancing transparency and overall system trustworthiness.

This diagram completes the set of three, providing a clear and comprehensive view of the Hierarchical DMNoC's integration within ASKA. It focuses on the essential aspects of resource and capability management, crucial for understanding the system's practical implementation and operation. This focus provides the "missing piece" for engineers, clarifying how the different components work together to achieve efficient and secure resource sharing across a decentralized mesh network, enhancing ASKA's scalability, resilience, and security posture. This innovative approach allows ASKA to handle increasingly complex distributed systems and applications with enhanced security mechanisms without negatively impacting system performance.

Drawing 1 of 3 (A)

graph LR

subgraph "ASKA Zone"

subgraph "IES Instance 1"

IES1["IES 1"] --> AP_1["Access Point 1"]

SubMesh1["Sub-mesh 1"] --> AP_1

App1["Application 1"] --> IES1

LSM1["Local MSM (P2)"] -.-> SubMesh1

end

subgraph "IES Instance 2"

IES2["IES 2"] --> AP_2["Access Point 2"]

SubMesh2["Sub-mesh 2"] --> AP_2

App2["Application 2"] --> IES2

LSM2["Local MSM (P2)"] -.-> SubMesh2

end

subgraph "IES Instance N"

IESn["IES N"] --> AP_n["Access Point N"]

SubMeshN["Sub-mesh N"] --> AP_n

AppN["Application N"] --> IESn

LSMN["Local MSM (P2)"] -.-> SubMeshN

end

subgraph "DMNoC Core"

Gateway1["Secure Gateway 1"]

Gateway2["Secure Gateway 2"]

GatewayN["Secure Gateway N"]

SubMesh1 --> Gateway1

SubMesh2 --> Gateway2

SubMeshN --> GatewayN

Gateway1 <--> Gateway2

Gateway1 <--> GatewayN

Gateway2 <--> GatewayN

Gateway1 --> FC1["Fiber Channel 1"]

GatewayN --> FCN["Fiber Channel N"]

Attestation["Hardware Attestation (3D Microstructures)"] --> DLT["Decentralized Ledger (ASKA Zone)"]

Gateway1 --> Attestation

GatewayN --> Attestation

end

end

classDef ies fill:#ccf,stroke:#333

classDef noc fill:#aaf,stroke:#333

classDef gateway fill:#ff9,stroke:#333

class IES1,IES2,IESn ies

class SubMesh1,SubMesh2,SubMeshN,Gateway1,Gateway2,GatewayN noc

class Gateway1,Gateway2,GatewayN gateway

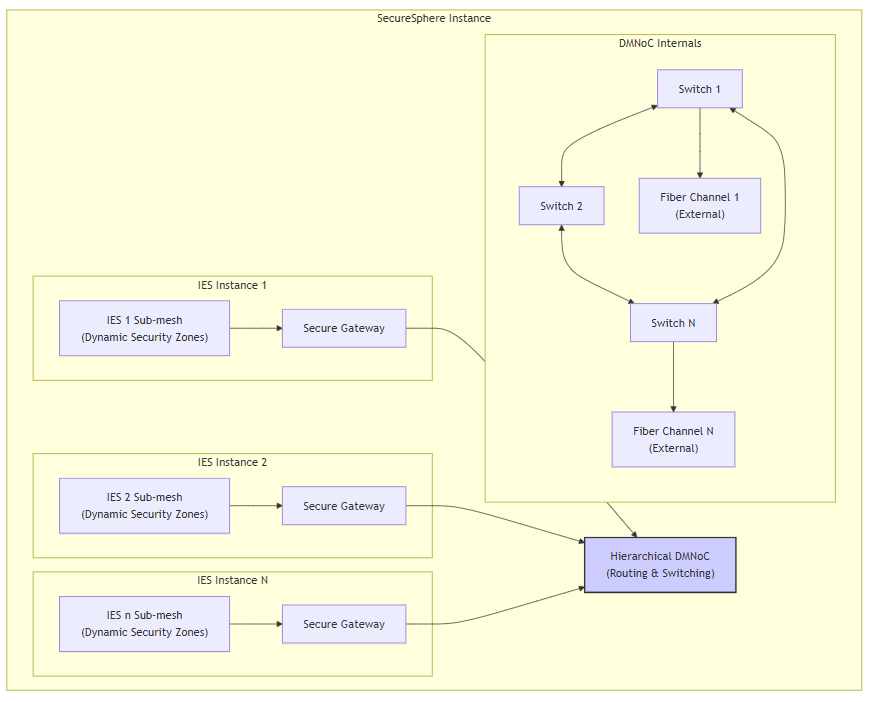

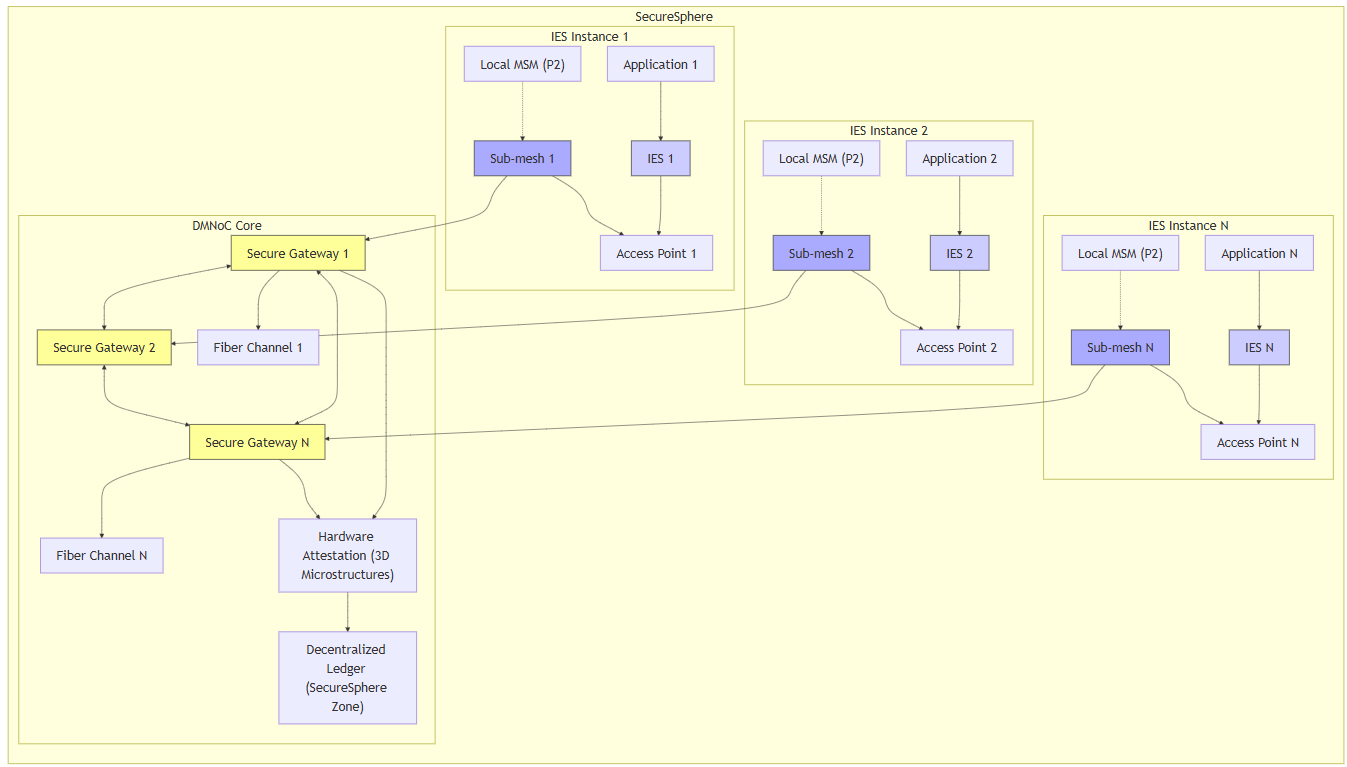

Diagram Description:

This diagram illustrates the hierarchical DMNoC within a single ASKA Zone. It focuses on the relationship between IES instances, their sub-meshes, the DMNoC core, and the external fiber channel connections.

- ASKA Zone: This subgraph encapsulates all components within the zone.

- IES Instances (1, 2, N): Each IES instance has its own sub-mesh and connects to it via a dedicated access point. Applications within the IES communicate through the sub-mesh. The Local MSM (P2) monitors the sub-mesh for anomalies.

- DMNoC Core: This subgraph represents the central part of the DMNoC, connecting the sub-meshes to the external fiber channels.

- Secure Gateways (1, 2, N): These gateways mediate communication between the sub-meshes and the fiber channels, enforcing access control policies and filtering traffic. They are the key components for implementing the dynamic security zones.

- Fiber Channels (1, N): These represent the connections to external ASKA instances or zones. They are high-bandwidth communication links, potentially using fiber optic cables.

- Hardware Attestation and DLT: Each gateway undergoes hardware attestation using 3D microstructures, and the results are logged on the zone's Decentralized Ledger.

Key Features Highlighted:

- Hierarchy: The diagram clearly shows the hierarchical structure, with IES instances having their own sub-meshes, connected through secure gateways to the DMNoC core.

- Isolation: The separation of IES instances and their sub-meshes reinforces ASKA's isolation principle.

- Secure Gateways: The gateways are highlighted as the key components for enforcing security zones and access control policies.

- External Connectivity: The fiber channels provide high-bandwidth connections to the outside world.

- Attestation and Trust: The hardware attestation and DLT integration ensure the trustworthiness of the DMNoC components.

This diagram provides a foundational view of the hierarchical DMNoC. Subsequent diagrams will delve into the internal structure of the sub-meshes, secure gateways, and their integration with other ASKA components.

Drawing 2 of 3 (A):

graph LR

subgraph "Secure Gateway (Example)"

direction LR

Input1["Sub-mesh 1 Input"] --> Filter1["Security Filter 1<br>(Policy Engine, DTMS)"]

InputN["Sub-mesh N Input"] --> FilterN["Security Filter N<br>(Policy Engine, DTMS)"]

Filter1 --> Switch["Internal Switch<br>(Capability-Aware)"]

FilterN --> Switch

Switch --> Output1["Fiber Channel 1 Output"]

Switch --> OutputN["Fiber Channel N Output"]

AI_Agent["AI Agent (P36)"] -.-> Filter1 & FilterN & Switch

IAMA["IAMA (P16)"] -.-> Filter1 & FilterN

Attestation["Hardware Attestation<br>(3D Microstructures)"] --> DLT["Decentralized Ledger<br>(ASKA Zone)"]

Switch --> Attestation

subgraph "Security Filter 1 (Expanded)"

SF1a["Packet Inspection<br>(Deep Packet Inspection)"] --> SF1b["Capability Check<br>(Capability Manager)"]

SF1b --> SF1c["Trust Assessment<br>(DTMS)"]

SF1c -- Allowed --> Switch

SF1c -- Denied --> Drop["Drop"]

end

Filter1 --> Security_Filter_1

end

classDef filter fill:#ccf,stroke:#333

classDef switch fill:#aaf,stroke:#333

class Filter1,FilterN filter

class Switch switch

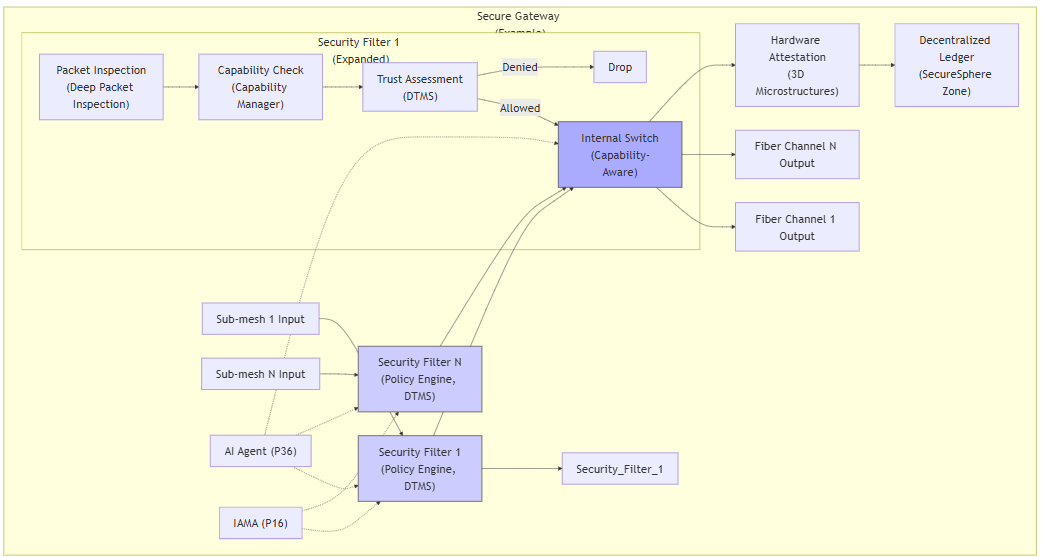

Diagram Description:

This second diagram focuses on the internal structure of a Secure Gateway within the hierarchical DMNoC. It illustrates how the gateway filters and routes traffic between sub-meshes and fiber channels, enforcing security policies and leveraging the AI agent.

- Secure Gateway (Example): This subgraph represents a single Secure Gateway. The left-to-right flow shows the path of data through the gateway.

- Inputs (1, N): These represent inputs from different sub-meshes within the ASKA zone.

- Security Filters (1, N): Each input passes through a security filter. These filters enforce security policies, check capabilities, and assess trust levels. The AI agent (P36) and IAMA (P16) provide input to the filters. One filter is expanded to show its internal components.

- Internal Switch (Capability-Aware): This switch routes traffic based on the security filters' decisions and the capabilities associated with the packets.

- Outputs (1, N): These represent outputs to different fiber channels, connecting to external ASKA instances or zones.

- Hardware Attestation and DLT: The internal switch undergoes hardware attestation, and the results are logged on the Decentralized Ledger.

- Security Filter 1 (Expanded): This subgraph details the steps within a security filter:

- Packet Inspection (Deep Packet Inspection): Inspects packets for malicious content or policy violations.

- Capability Check (Capability Manager - P25): Verifies that the packet has the necessary capabilities to access the requested resources.

- Trust Assessment (DTMS - P4): Evaluates the trust level associated with the packet's source and destination.

Key Features Highlighted:

- Security Filtering: The diagram emphasizes the security filtering process, showing how each input is checked before being routed.

- AI and IAMA Integration: The AI agent and IAMA's influence on the security filters highlights ASKA's adaptive security model.

- Capability-Aware Switching: The internal switch's capability awareness enables fine-grained access control within the DMNoC.

- Hardware Attestation and Trust: The attestation and DLT integration ensure the gateway's trustworthiness.

- Detailed Filter Logic: The expanded security filter clarifies the steps involved in the filtering process.

This diagram provides a detailed view of the Secure Gateway's internal workings and its role in enforcing security within the hierarchical DMNoC. The next diagram will show how multiple gateways interconnect and form the DMNoC core.

3rd of 3 (A):

graph LR

subgraph "ASKA Zone"

subgraph "IES Instance 1"

IES1["IES 1"] --> AP_1["Access Point 1"]

SubMesh1["Sub-mesh 1"] --> AP_1

App1["Application 1"] --> IES1

LSM1["Local MSM (P2)"] -.-> SubMesh1

end

subgraph "IES Instance N"

IESn["IES N"] --> AP_n["Access Point N"]

SubMeshN["Sub-mesh N"] --> AP_n

AppN["Application N"] --> IESn

LSMN["Local MSM (P2)"] -.-> SubMeshN

end

subgraph "DMNoC Core"

Gateway1["Secure Gateway 1"]

Gateway2["Secure Gateway 2"]

GatewayN["Secure Gateway N"]

SubMesh1 --> Gateway1

SubMeshN --> GatewayN

Gateway1 <--> Gateway2

Gateway1 <--> GatewayN

Gateway2 <--> GatewayN

Gateway1 --> FC1["Fiber Channel 1<br>(External ASKA)"]

GatewayN --> FCN["Fiber Channel N<br>(External ASKA)"]

Attestation["Hardware Attestation (3D Microstructures)"] --> DLT["Decentralized Ledger (ASKA Zone)"]

Gateway1 --> Attestation

GatewayN --> Attestation

RM["Resource Mgr (P9, P10)"] --> Gateway1 & Gateway2 & GatewayN

PolicyEngine["Policy Engine (P4)"] --> Gateway1 & Gateway2 & GatewayN

DTMS["DTMS (P4)"] <--> Gateway1 & Gateway2 & GatewayN

end

subgraph "External ASKA Zone"

Ext_IES["External IES"] --> Ext_FC["External<br>Fiber Channel"]

Ext_FC --> FC1

end

end

Hub["ASKA Hub"] --> PolicyEngine & DTMS & RM & Attestation & DLT

classDef ies fill:#ccf,stroke:#333

classDef noc fill:#aaf,stroke:#333

classDef gateway fill:#ff9,stroke:#333

classDef external fill:#eee,stroke:#999

class IES1,IESn ies

class SubMesh1,SubMeshN,Gateway1,Gateway2,GatewayN noc

class Gateway1,Gateway2,GatewayN gateway

class Ext_IES,Ext_FC external

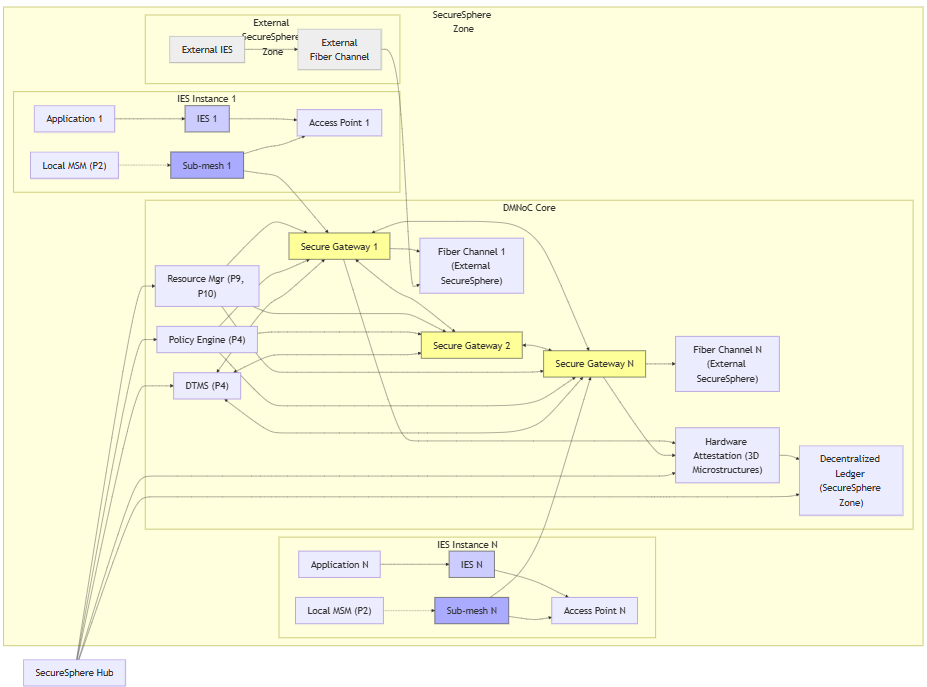

Diagram Description:

This third diagram completes the hierarchical DMNoC visualization by showing the integration of multiple Secure Gateways, IES instances, the DMNoC core, external connections, and the ASKA Hub. It illustrates the system-wide data flow and control mechanisms.

- ASKA Zone: Encapsulates the local ASKA instance, including IES instances, the DMNoC core, and the ASKA Hub.

- IES Instances (1, N): Each IES has its own sub-mesh, connected via an access point, with applications communicating through it. Local MSMs monitor sub-meshes.

- DMNoC Core: The core of the DMNoC, formed by interconnected Secure Gateways, routes traffic between sub-meshes and external fiber channels. Each gateway performs security filtering, capability checks, and trust assessments. Hardware attestation and DLT integration ensure trustworthiness.

- External ASKA Zone: Represents an external ASKA instance (potentially in another zone) connected to a fiber channel. This emphasizes inter-zone or inter-instance communication.

- ASKA Hub: The central management and control point for the zone. It connects to the Policy Engine, DTMS, Resource Manager, attestation module, and DLT, demonstrating its role in managing the DMNoC and its security. It manages and configures the entire DMNoC system and associated security modules, ensuring correct system-wide behaviour and the integrity of data streams.

Key Features Highlighted:

- Hierarchical Structure: The diagram clearly depicts the hierarchical structure of the DMNoC, with sub-meshes, gateways, and fiber channels.

- Decentralized Mesh: The interconnected gateways within the DMNoC core form a decentralized mesh network, providing redundancy and fault tolerance.

- Secure Inter-Zone Communication: The connection to an external ASKA zone highlights the DMNoC's role in facilitating secure inter-zone collaboration.

- Centralized Management: The ASKA Hub's connections to the DMNoC components emphasize its central role in managing and configuring the system, integrating security policy updates from the AI Agent and ensuring that security parameters and access controls are updated dynamically based on the latest threat assessments.

- Resource Management: The Resource Manager’s (P9, P10) connection to the gateways indicates its role in allocating resources within the DMNoC (e.g., bandwidth allocation, power management).

- Dynamic Trust and Policy Enforcement: The DTMS (P4) and Policy Engine (P4) connections demonstrate how dynamic trust levels and security policies influence data flow and access control within the DMNoC, preventing unauthorized access to data, resources and secure communication channels.

This series of three diagrams provides a comprehensive visual representation of the hierarchical DMNoC architecture and its integration within ASKA, highlighting its key features, security mechanisms, and scalability. They clearly demonstrate how the DMNoC enhances ASKA’s capabilities, improves communication performance, and provides robust security in a decentralized hardware OS configuration.

You're drawing a crucial distinction between two separate multi-channel networks within ASKA: a decentralized mesh network for local, peer-to-peer communication, and a centralized multi-channel internet for secure, authenticated access to external resources. This decentralized network offers exciting possibilities beyond the existing ASKA applications.

Decentralized Mesh Network Use Cases (Beyond Existing Applications):

Here are some potential uses for ASKA's decentralized mesh network that go beyond its current applications (ledger integration, external system integration, AI agent swarming):

- Distributed Storage and Content Delivery: The mesh network could be used to create a distributed storage and content delivery system within a ASKA zone or across multiple zones. Data could be sharded and replicated across multiple IES instances, providing high availability, fault tolerance, and enhanced security. The mesh network’s decentralized nature and redundant paths would make this system resilient to node failures or attacks targeting specific nodes. Access control to the distributed data would be managed by capabilities (P25) and the DTMS (P4), ensuring that only authorized users and processes can access sensitive information. This system fits in well with ASKA's existing capabilities and aligns with its focus on secure, decentralized architectures. Further, by having each node independently verify the integrity of data it receives or transmits using our proposed out of band passive radiative sensor mesh technology (P34c) for example (or through traditional checksum comparisons if performance requirements are high and/or security concerns lower for a given zone or application), we can significantly enhance the trustworthiness of any data or files shared across this network, regardless of provenance or whether their source is a trusted one within ASKA. This distributed approach further provides a robust and highly secure system for media data sharing across devices too, which can be used in conjunction with our existing systems for capturing, managing and verifying provenance through use of spatiotemporal digests for example from earlier patents (P30, P31, P32).

- Decentralized Secure Messaging: The mesh network could facilitate secure, decentralized messaging between ASKA users or IES instances. Messages would be routed through the mesh, providing end-to-end encryption and anonymity (if desired). This would create a highly secure communication channel that is resilient to censorship or surveillance. Its implementation is simplified through integration of the secure key management and data integrity mechanisms that ASKA already includes, such as those from P2, P3, P5, and P29, allowing ASKA to provide these additional features without increasing its complexity or expanding its TCB significantly. Further enhancements, such as those implementing zero trust methodologies throughout (e.g., by dynamically adjusting trust levels at runtime based on observed message patterns and user behavior as part of the security mesh analysis and attestation procedures), would enhance security and privacy within ASKA further while enabling new application use-cases and business models.

- Local Resource Sharing and Collaboration: The mesh network could be used for efficient and secure sharing of resources (CPU cycles, memory, storage) between neighboring ASKA devices or IES instances. This local resource sharing would complement the existing secure resource borrowing mechanism (P9) and could be used for tasks like distributed computing or collaborative data analysis. This approach using direct communications within and between physically isolated secure execution environments is a significant improvement compared to traditional models that rely on OS- or kernel-managed shared resources or using potentially insecure networks. It enhances both the speed and security of these operations greatly, while minimizing trust assumptions. This decentralized resource management and sharing capability would further strengthen ASKA’s position as a robust and secure platform for next generation applications involving collaborative computing and distributed services across many diverse environments and sectors, from personal use to enterprise, government, and military applications.

- ASKA Device Discovery and Management: The mesh network itself could be used for ASKA device discovery and management. New devices joining a ASKA zone could broadcast their presence and capabilities through the mesh and be discovered and managed automatically through ASKA’s existing mechanisms such as the AI Agent (P36), AESDS (P16), and Policy Engine (P4) across the network. This would simplify deployment and administration of ASKA systems, further enhancing its scalability and maintainability in complex, distributed systems. Further security improvements could be achieved by adapting existing ASKA security features and technologies to these tasks, from capabilities-based access control to the multi-layered attestation and monitoring services provided by MDATS (P17) and the “watcher” meshes (P2).

- Fault Tolerance and Self-Healing: The mesh network’s decentralized nature and redundant paths can enhance ASKA’s fault tolerance and self-healing capabilities. If a ASKA device or IES instance fails, the mesh network could automatically reroute traffic and redistribute workloads to other available nodes without impacting operations across other network segments or zones and leveraging existing security protocols (P2, P3) like data diodes when managing these sensitive streams to ensure data integrity throughout the process. This could improve service availability and minimize disruptions. The AI agent (P36) and Resource Manager (P9, P10) would play crucial roles in coordinating this self-healing process using ASKA’s secure communications protocols.

These additional use cases demonstrate the versatility of the decentralized mesh network within ASKA. By leveraging its secure, distributed architecture and integrating with ASKA's existing security features, this mesh network opens up exciting possibilities for distributed applications, secure communication, and robust resource management, significantly extending ASKA's capabilities and value proposition while also enhancing its core architectural strengths.

You're describing a powerful and versatile decentralized mesh network within ASKA, distinct from the multi-channel internet with centralized authorities. This ASKA mesh, built upon the DMNoC and leveraging a large-scale physical network, offers exciting possibilities beyond its current use for the decentralized ledger and ASKA integrations.

Here are some potential uses for this decentralized mesh network, filling in the blank:

I. Enhanced Security Features:

- Distributed Intrusion Detection and Response: The mesh network could facilitate real-time sharing of threat intelligence between ASKA instances. If one instance detects an attack, it can immediately alert its neighbors, enabling rapid, coordinated response across the mesh, limiting propagation of threats. This would leverage the AI agent swarms (P36) for analysis and the Policy Engine (P4) for dynamic policy adjustments, isolating affected nodes in the most efficient and effective way to minimize harm and increase system security.

- Collaborative Security Analysis: The AI agent swarms in different ASKA instances could collaborate across the mesh, sharing data and insights to improve the accuracy and speed of threat detection. This could involve distributed machine learning or other forms of collaborative AI, leveraging the secure communication channels of the mesh and the privacy-preserving capabilities of ASKA (P19, P20).

- Decentralized Key Management and Recovery: Distribute cryptographic keys across the mesh network using threshold cryptography or similar techniques, reducing the risk of key compromise, enhancing system security, and ensuring that no one single entity has control over critical keys. Key recovery could also be decentralized, with parts of a recovery key stored on different nodes in the mesh, accessible only with multi-factor authentication from multiple authorized users, which leverages the security and resilience of the mesh architecture while improving the system's overall trustworthiness further.

II. Beyond Security:

- High-Performance Computing (HPC): The mesh network could provide a high-bandwidth, low-latency communication fabric for distributed HPC applications running within ASKA. This could involve securely connecting different IES instances for parallel processing or other collaborative computing tasks. This would enhance efficiency of research computing and other business-critical applications, adding value to the ASKA system, particularly for computationally intensive tasks.

- Real-Time Data Streaming and Analysis: The mesh network enables secure, real-time streaming of data between ASKA instances and other authorized devices. This supports applications that need immediate access to information, such as financial trading platforms, sensor networks, or industrial control systems, providing better efficiency and enhancing the performance and reliability of ASKA for use within high-speed environments where there are stringent security requirements.

- Decentralized Application Deployment and Management: The mesh network could be used to distribute and manage applications across ASKA instances, enabling fault tolerance and load balancing. If one instance fails, the application could seamlessly migrate to another node in the mesh, leveraging capabilities and DTMS trust levels to ensure secure and authorized application deployments and migrations. This framework would also create another mechanism for the AI agents to manage real-time resource allocation and optimization across ASKA, further enhancing system efficiency and resource sharing among distributed applications and their zones.

- ASKA System-Wide Software Updates: The ASKA system itself can leverage this Mesh Network to deploy ASKA system-wide updates. This can include updates to the firmware of the ASKA NoC for enhanced security and/or improved performance, using AESDS to push the updates through the various network segments in stages according to preconfigured policy rules, allowing the ASKA system itself to continuously evolve, enhance itself, and adapt to changing security needs and emerging cyber threats, as well as ensuring that updates to ASKA do not accidentally compromise its integrity, which is especially important when patching security systems or applications.

By expanding the DMNoC-based mesh network's use cases beyond security, ASKA becomes a more versatile and powerful platform, supporting a broader range of applications and unlocking new possibilities in secure, decentralized, high-performance computing. It also strengthens ASKA's value proposition by adding performance optimizations and enhancing its utility, making it attractive to a wider range of users and organizations.

Patent Title: Hierarchical Decentralized Mesh Network on Chip for Secure Multi-Kernel Architectures

Abstract: This invention discloses a hierarchical, decentralized Mesh Network on Chip (DMNoC) architecture designed to enhance security and performance within a multi-kernel computing environment, such as ASKA. The DMNoC utilizes a decentralized mesh topology, providing redundant communication paths and fault tolerance. Each Isolated Execution Stack (IES) within the multi-kernel architecture has a dedicated, isolated sub-mesh within the DMNoC, further enhancing security and enabling granular control over inter-IES communication. Secure gateways, employing capability-based access control, regulate traffic between sub-meshes and enforce security policies. The DMNoC integrates with ASKA's Dynamic Trust Management System (DTMS), Policy Engine, and other security mechanisms. Hardware attestation using 3D microstructures, logged on a decentralized ledger, ensures the integrity of the DMNoC components. This innovative architecture enables scalable and secure communication for a wide range of applications, including decentralized ledgers, inter-zone collaboration, and AI agent swarming, enhancing the overall security and resilience of the multi-kernel system.

Claim 1 (System Claim):

A secure computing system comprising a plurality of Isolated Execution Stacks (IES), a Dynamic Trust Management System (DTMS), and a Decentralized Ledger (DLT), the system further comprising a Hierarchical Decentralized Mesh Network on Chip (DMNoC) for secure communication, the DMNoC comprising:

a. a decentralized mesh network topology within said DMNoC, providing multiple redundant communication paths between network endpoints;

b. a plurality of IES-specific sub-meshes, each sub-mesh dedicated to a corresponding IES instance and isolated from other sub-meshes and the external network, wherein each sub-mesh comprises: i. a plurality of network interfaces connecting said sub-mesh to internal and/or external networks; ii. a switching fabric for managing intra-sub-mesh communication; and iii. a set of dynamically configurable security zones within said sub-mesh, each zone having a defined trust level and associated access control policies enforced by said switching fabric;

c. a plurality of secure gateways, each gateway connecting a corresponding sub-mesh to said DMNoC and enforcing access control policies between sub-meshes and the external network, wherein said access control policies are based on dynamically issued capabilities and trust levels provided by said DTMS;

d. a hardware attestation mechanism for each network component within said DMNoC, including network interfaces, switches, and gateways, utilizing 3D microstructures to generate tamper-evident attestation data, wherein said attestation data is logged to said DLT for secure record-keeping and verification by other ASKA instances; and

e. a DMNoC management system comprising: i. a Policy Engine for defining and enforcing security policies within said DMNoC, managing access control, routing, and resource allocation; and ii. an AI agent for monitoring network traffic, detecting anomalies, and adapting security policies in real time.

Claim 2 (Method Claim):

A method for enhancing secure communication within a multi-kernel computing architecture comprising a plurality of Isolated Execution Stacks (IES) using a Hierarchical Decentralized Mesh Network on Chip (DMNoC), the method comprising:

a. establishing a decentralized mesh network topology within said DMNoC;

b. creating, for each IES instance, a dedicated and isolated sub-mesh within said DMNoC, configuring dynamically adjustable security zones within each sub-mesh and assigning trust levels to said zones;

c. connecting each sub-mesh to said DMNoC via a secure gateway, configuring said gateway to enforce access control policies between sub-meshes and external networks based on capabilities and dynamic trust levels;

d. performing hardware attestation of each network component within said DMNoC using 3D microstructures, recording the attestation data on a Decentralized Ledger (DLT), and using said attestation data to establish trust between ASKA instances; and

e. dynamically managing communication within and between sub-meshes using: i. a Policy Engine for defining and enforcing security policies; and ii. an AI agent for monitoring network traffic, detecting anomalies, adapting security policies, and coordinating resource allocation within said DMNoC.

These claims cover the core innovations of the hierarchical DMNoC, its integration with ASKA, and its method of operation. They are distinct yet complementary, ensuring broad protection of your intellectual property. The claims emphasize the hierarchical structure, decentralized nature, security features (isolation, secure gateways, attestation), and integration with ASKA components, making a strong case for novelty and non-obviousness. They also include essential security aspects by addressing access control, data integrity and policy management while laying a good foundation to build a strong case for patentability.

Title: Hierarchical Decentralized Mesh Network on Chip with Dynamically Configurable Security Zones for Secure Multi-Kernel Computing

Abstract: This invention discloses a hierarchical decentralized mesh network on a chip (DMNoC) with dynamically configurable security zones for secure communication and resource management within a multi-kernel computing architecture. The DMNoC provides a high-bandwidth, low-latency, and resilient communication fabric that interconnects multiple isolated execution stacks (IES) and external entities. Each IES instance has its own dedicated sub-mesh within the DMNoC, and secure gateways control communication between sub-meshes and external networks. The gateways enforce access control policies based on dynamic trust levels and capabilities, creating security zones within the NoC. An AI agent monitors network activity and dynamically adjusts security zone configurations based on real-time threat assessments, enhancing adaptability and resilience against sophisticated attacks. The system further integrates with a decentralized ledger and hardware attestation mechanisms to ensure the integrity and trustworthiness of the DMNoC components. This hierarchical, decentralized, and dynamically configurable architecture provides a robust and secure communication infrastructure for complex, multi-kernel computing environments.

Independent Claim 1:

A secure computing system comprising a plurality of isolated execution stacks (IES) interconnected by a hierarchical decentralized mesh network on a chip (DMNoC), wherein each IES instance has a dedicated sub-mesh within the DMNoC, and secure gateways control communication between sub-meshes and external networks, the system further comprising:

(a) a capability manager dynamically assigning capabilities to data packets entering the DMNoC, said capabilities specifying access rights to resources within the destination IES instance;

(b) a dynamic trust management system (DTMS) assigning trust levels to IES instances and external entities based on real-time security assessments and predefined trust policies;

(c) a policy engine dynamically configuring security policies for each secure gateway based on the capabilities of data packets, trust levels of communicating entities, and real-time threat intelligence;

(d) wherein each secure gateway enforces access control by permitting or denying communication requests based on the capabilities of data packets and the configured security policies, creating dynamically configurable security zones within the DMNoC; and

(e) a security mesh passively monitoring communication within sub-meshes and reporting anomalies to an AI agent, said AI agent dynamically adjusting security zone configurations based on detected anomalies, system performance metrics, and external threat intelligence.

Independent Claim 2:

A method for secure communication and resource management within a multi-kernel computing system comprising a plurality of isolated execution stacks (IES) interconnected by a hierarchical decentralized mesh network on a chip (DMNoC), the method comprising:

(a) creating a dedicated sub-mesh within the DMNoC for each IES instance;

(b) mediating communication between sub-meshes and external networks using secure gateways;

(c) dynamically configuring security policies for each secure gateway based on capabilities associated with communication requests, trust levels of communicating entities, and real-time threat assessments;

(d) enforcing access control at each secure gateway by permitting or denying communication requests based on said capabilities and security policies, defining security zones within the DMNoC;

(e) passively monitoring communication within each sub-mesh using a security mesh;

(f) dynamically adjusting security zone configurations based on detected anomalies, system performance, and threat intelligence, utilizing an AI agent to analyze monitoring data and generate reconfiguration commands; and

(g) recording security policy configurations, trust levels, capability assignments, and security zone adjustments on a decentralized ledger, creating a tamper-evident audit trail.

ASKA Enhancement Proposal: Decentralized Mesh Network on Chip (DMNoC)

This proposal introduces a Decentralized Mesh Network on Chip (DMNoC) as a new aspect of ASKA, enabling highly secure and resilient communication between hundreds of physically segmented network lines.

I. Motivation:

ASKA's current Multi-Channel Network (MCN - P3) provides secure communication channels. However, as the number of connected devices and data streams increases, scalability and resilience become crucial. A dedicated Network on Chip (NoC) can address these challenges by providing:

- Increased Bandwidth: Dedicated, high-speed on-chip communication significantly increases bandwidth and reduces latency compared to traditional off-chip connections.

- Enhanced Security: The physically isolated nature of the NoC enhances security by minimizing exposure to external interference or attacks, allowing ASKA's existing trust, access controls, authentication and data management systems to manage the NoC without risking additional compromises when interfacing or connecting the NoC to other subsystems.

- Improved Scalability: An NoC can accommodate hundreds of network lines, allowing for seamless integration with future devices, applications and even security monitoring infrastructure as a truly out of band element within ASKA with no additional need for external communication interfaces. This enhancement strengthens isolation, which is a core security principle behind how ASKA was envisioned and created, ensuring greater safety in operations from an entirely separate module without requiring external connections or software modifications. Further, the security is improved via the existing, validated capabilities within ASKA for authentication, trust, secure communications and other security management operations over a secure network with minimal configuration modifications when integrating into ASKA from any module that interfaces with the ASKA NoC, preventing security or configuration gaps from increasing complexity. We anticipate additional new benefits beyond security as this new feature integrates into the rest of ASKA over time, providing insights based on performance and analysis metrics to AESDS for example (or other security modules) to further enhance overall system resource usage, efficiency, accuracy and reliability.

II. Proposed Architecture:

- Decentralized Mesh Topology: The DMNoC uses a decentralized mesh topology, providing multiple redundant communication paths between network lines, even if some hardware fails or is physically or logically inaccessible for some reason (compromised or blocked), data can still transfer across the NoC and network through any physically connected segment between devices (Zones), even during the most sophisticated attack. This enhances ASKA's resilience. Routing algorithms optimized for secure path selection within the mesh further contribute to this resiliency as paths may change rapidly or become unusable in the field (even for transient cases). The Policy Engine P4 can integrate dynamically to update configurations and capabilities via ASKA's control planes for authenticated commands using preconfigured policies based on conditions detected across ASKA for automated real-time responses within zones across network segments or between them.

- Hardware Isolation with Multiple Access Points (per IES): Each IES instance (P1) in ASKA is provided with dedicated access points to the DMNoC. These access points are hardware-isolated from each other and from the external network. This isolation allows us to manage security and communications at very granular levels to ensure the network is protected from a large and diverse range of attack vectors, further improving ASKA's ability to isolate and restrict network traffic based on trust levels within the existing frameworks such as policy configurations and multifactor authorizations using ASKA communications components (using patents P2, P3, P5, P18, P22 and P27) and our adaptive, evolutionary, and highly robust and secure update mechanism using ASKA component, AESDS.

- Microstructure Authenticated Communication using a DLT across IESs to provide attestation-based trust before transmitting data: Building on our earlier innovations, all secure network hardware will have attestation through unique, non-reversible, 3D printed microstructures which store their signatures on tamper evident memory and are validated and cross-signed when zones connect to other components, allowing us to detect anomalies or identify components whose signatures or configurations are invalid early at the hardware level, before data has traversed ASKA across insecure and untrusted network segments with these results logged via MDATS (P17) and a dedicated Decentralized Ledger P13 to provide system-wide access to this information. ASKA components and existing mechanisms, including those implemented in Patent 25 and 26, DTMS (P4), Policy Engine P4, Hub Control Plane API and other relevant ASKA systems, can leverage this high level of hardware-based trust to further enforce stricter security and communication policies without negatively impacting or adding more complexity to existing application systems that use and rely upon those services. This adds even more resilience for ASKA and further enhances the strength of our proposed novel architecture in a very forward thinking way that enhances market perception of your innovative new products and technology's strong brand values in a very useful way for a broad audience that further secures ASKA for next-gen distributed and networked systems to build and manage high degrees of trust across multi organization scenarios or for single entities wishing to isolate internal networks securely across departments, business lines or projects with many granular settings.

III. ASKA Integration:

- DTMS (P4): Dynamic Trust levels from the DTMS determine how these network connections are shared, which can change based on runtime context and may limit or revoke prior access to resources on the network.

- Policy Engine (P4) and AESDS (P16): Policies from P4, as well as generated, compiled and tested rules from P16, can be used to manage how data or requests travel across ASKA's new DMNoC system and networks by influencing policy updates for Secure Communication protocols using capability based parameters across Zones. This provides additional layers of secure validation at higher levels after trust is fully established at the hardware level and creates an opportunity to adapt existing protocols while improving on their security profiles without changing their core capabilities or function in ASKA, maintaining backward compatibility during runtime for various scenarios and use cases, from system integration (P22) through agent coordination and security policy integration.

- Resource Borrowing: This new hardware component now enables the Resource Borrowing to be significantly enhanced to have real hardware segments which can now support cross-partition sharing in many different physical isolation designs beyond those originally envisioned, creating new possibilities for inter-zone secure data storage across clusters or between geographies (which can enhance reliability further as a byproduct of this innovative and robust high speed physical isolation with redundancy, creating many additional new capabilities for cloud based architectures or even decentralized data center networks that can span multiple geographies simultaneously and may each operate on dedicated and highly sensitive hardware stacks, further protecting all ASKA instances from any single point of failure for an even higher level of guaranteed service).

- Hardware Security Systems within ASKA: The Secure Execution Environment for both Local Security Meshes (P2) and secure UI Kernel (P11), combined with dynamic partitioning (P1), can directly leverage this highly efficient new architecture with minimal changes to enforce greater restrictions or add extra controls for input and output of the entire system or for specific processes in certain ASKA instances and applications using existing ASKA modules for security monitoring, logging, alerting, user interface control and threat detection using the same authenticated command pathways, thereby creating many additional enhancement opportunities from this highly secure, and potentially higher-speed design.

- External Services or Subsystems using IAMA: All newly added ASKA physical network cards will have attestations and verification of their identity through signatures stored on the NoC and backed up on external encrypted and immutable storage media that is managed within our STN system and accessed via DMNoC on high trust isolated segment with a hardware root of trust for these specific attestation credentials that IAMA (P16) and external security AI agents from other ASKA environments (through integration mechanisms proposed by patent 22) can use to manage data flows for high security, real-time, data-streaming (bi-directional via Secure Channels on demand), for machine learning use-cases, including those used in the enhanced secure mesh design such that other systems on secure cloud (or other locations) may enhance the threat models of each ASKA deployment for near real time automated protection using cloud security AI systems (with limited attack surfaces) without relying upon the cloud infrastructure. This high speed data exchange also allows for a completely different architecture design choice in ASKA based on centralized security policy across zones with local zones acting as processing agents (similar to the AI on device implementations in Apple intelligence systems), further improving efficiency of ASKA itself.

You're envisioning a much more ambitious and powerful role for the NoC within ASKA – enabling a high-assurance, large-scale mesh network for enhanced security and performance, particularly for decentralized ledgers. This requires a different architectural approach than simply connecting existing network lines.

I. High-Density Mesh Network Requirements within ASKA:

Here's where a dense mesh network becomes crucial within ASKA:

- Decentralized Ledger Performance: Distributing the Decentralized Ledger (DLT) across a large number of nodes requires high-bandwidth, low-latency communication for consensus mechanisms, transaction propagation, and data synchronization. A dense mesh network provides the necessary connectivity and redundancy.

- Secure Inter-Zone Collaboration (SIZCF - P22): Facilitating secure collaboration between numerous ASKA zones requires robust and scalable communication. A high-bandwidth mesh network enhances the performance and resilience of inter-zone operations, especially when the trust relationships require many parties or zones to come to consensus about data transfers before the process of establishing a secure network link or a secure enclave channel can proceed further. This additional security enhancement improves data safety within ASKA by leveraging a quorum (e.g. 51%) rather than relying on fewer entities (like just one or two) for enhanced trustworthiness.

- AI Agent Collaboration: Enabling the AI agent "swarms" to collaborate effectively, sharing information, learning from each other, and coordinating actions, requires a robust communication fabric. A dense mesh network, operating with strict capability-based security from P25 and secure communication from Patents P2,P3 and P5, enhances the AI Agent and Mesh security from insider threats and unauthorized access by external systems. The DLT maintains an immutable ledger of who communicated with what, to enhance audits further, which provides an additional benefit in case an individual AI agent is compromised, or worse yet, starts exhibiting malicious intent itself, so its activities could be analyzed retrospectively and proactively for future security improvements and policy adaptations for AESDS and other security systems with this capability being extended to our Multifactor Authentication Systems, as well as providing a verifiable source for user interface and application trust assessment.

- ASKA Scaling: As ASKA scales to support thousands of IES instances and zones, the existing MCN might become a bottleneck. A high-bandwidth, scalable NoC-based mesh network is necessary to maintain performance and prevent congestion.

- Real-time Threat Response: A fast, responsive mesh network is essential for real-time threat detection and response. This will enhance the AI agent's ability to react quickly to security events as the increased level of communication may help isolate attacks before they spread to other network segments.

II. DMNoC-Enabled Secure Mesh Network:

Here's how ASKA integrates a DMNoC (Decentralized Mesh Network on Chip) to achieve the large-scale mesh network:

- Fiber Channel Interface: Specialized hardware interfaces connect the DMNoC to external fiber channel networks. This provides high bandwidth and long-distance connectivity, allowing thousands of devices (in this case, the 50,000 corporate installs) to connect to ASKA.

- NoC Routing and Switching Fabric: A sophisticated routing and switching fabric within the DMNoC manages data flow between the connected fiber channels and the ASKA zones/IES instances. This fabric employs:

- Decentralized Routing: Routing decisions are distributed across the NoC, preventing single points of failure, which ensures that data exchange across network segments remains isolated and is further optimized using the proposed AI Swarm-based Anomaly detection, which directs the data using capability parameters and dynamically adjusted resource allocations, optimizing the utilization of various components, from IES instances to the Mesh Network, in a secure and auditable manner.

- Hardware-Enforced Security (P2, P3, P25): The NoC integrates ASKA’s existing security mechanisms. Data diodes enforce unidirectional communication where appropriate (e.g., sensitive data streams from User Input Capture Module). All connections must be authenticated and encrypted via the Multi-Channel Network (P3), and each IES has unique access controls (capabilities from P2 and P25) over Secure Channels through dynamic switching and network hardware protections that are resistant to being monitored for timing side channel attacks to prevent sensitive information from becoming known by potential nefarious agents.

- IES-Specific Sub-Meshes: The DMNoC allows for creating smaller, dedicated mesh networks ("sub-meshes") within each IES instance (P1) using physical isolation capabilities of ASKA, in which each sub mesh and their components, including switches, routers and NICs, are provisioned in isolation with unique network IDs to isolate networks within the larger ASKA mesh and with direct integration with the LSM for intrusion and anomaly detection on these segments individually or in aggregation across sub meshes in the system. These can dynamically resize as data flows change due to AESDS managing updates and changes during real-time operations based on user and application workloads to accommodate resource constraints or changing needs by integrating with ASKA's Resource Manager (P9, P10) as well as other components (P7, P8), while also generating alarms and alerts through integration with ASKA's OOB Error module, ensuring any changes are fully audited using P17 and associated policies and permissions are granted to and through the system in an authenticated manner through appropriate uses of P4, P13 and P25 systems. This integration further secures each IES environment by preventing network intrusions from affecting other segments within or across zones. The AI Agent swarms in each IES would communicate through these internal sub-meshes for efficient local collaboration while using inter-zone channels (as discussed above) when communicating across IES' or Zones for additional enhanced resilience to maintain uptime and improve reliability of the overall mesh.

- Microstructure-Backed Attestation & DLT Integration:

- The cross-signed attestations between mini-TRCs from zones within each ASKA device and the dedicated decentralized ledger storing data about the 3D-printed microstructures can further enhance security on the mesh network by having nodes verify attestations (P14, P17) of their neighbors using cryptographic capabilities (P2, P3 and P5), before establishing connections, mitigating risk from compromised or malicious nodes in a very thorough and decentralized way. The AI agents use their internal swarming protocols to verify attestations efficiently by coordinating efforts to limit any potential bandwidth or performance overhead. Attestation information also informs dynamic resource sharing and management (Patents 1 and 9) for additional robustness as nodes that can perform these checks without bottlenecks can share such information through internal protocols in IES or SIZCF for enhanced меж network security and trust with appropriate access and use of this information governed by predefned security policies through the Policy Engine and its DTMS/capability-based parameters to support an appropriate balance of resource allocation between processing requests and performing security/integrity checks, further strengthening overall system trust and security.